# ЭЛЕКТРОНИКА

Лектор:

к.ф.-м.н. Алимгазинова Назгуль Шакаримовна

# Основы цифровой электроники

Электронные устройства

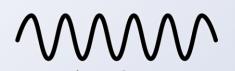

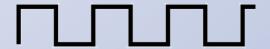

Цифровой сингал

#### Аналоговые устройства

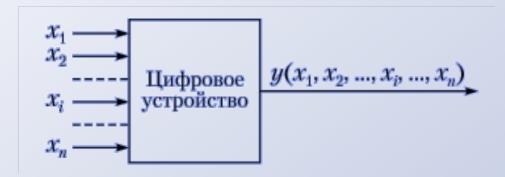

Цифровые устройства (ЦУ)

Это преобразователи электрических сигналов с непрерывно изменяющимися во времени токами и напряжениями

Это устройства, которые выполняют функции формирования, преобразования и передачи информации имеющей вид двоичного кода, т.е. совокупности «нулей» и «единиц».

#### СИСТЕМЫ СЧИСЛЕНИЯ

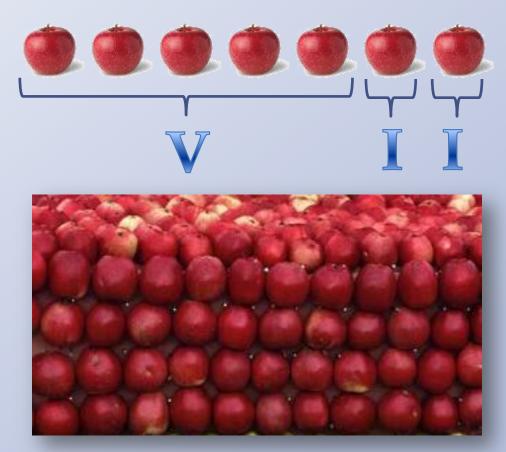

#### Римская система счисления

Число = сумма значений разных значков

$$I-1$$

$V-5$

$X-10$

$L-50$

$C-100$

$M-1000$

**1258 яблок** → **МССТУП** яблок

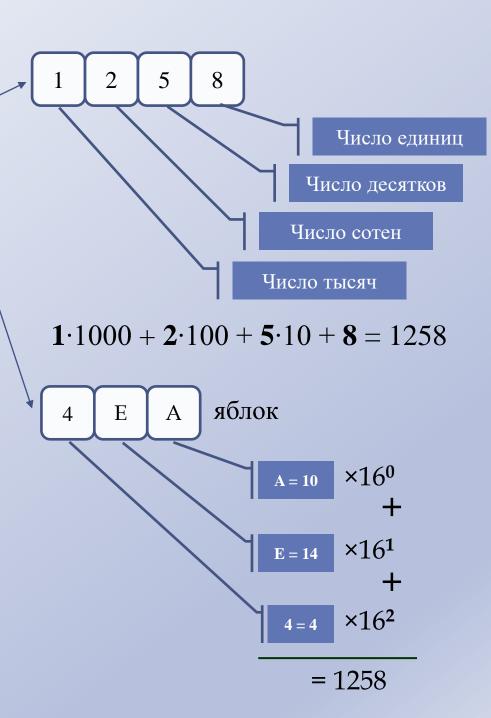

# <u>Десятичная система</u> <u>счисления</u>

1258 яблок

# **Шестнадцатеричная** система счисления

В шестнадцатеричном виде числа записываются с помощью последовательности значков 0-9 и A-F

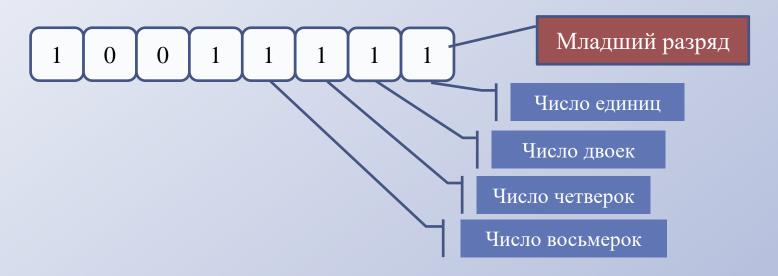

## Двоичная система счисления

**Двоичная** система использует всего **два знака** для записи чисел. Соответственно, **младший** разряд хранит число **единиц**, следующий за ним — число **двоек**, следующий — число **четверок** и т. д. Что хранит **старший** разряд — зависит от разрядности.

$$9 + 5.10 + 1.100 = 159 -$$

это десятичная запись числа

$$1 + 1 \cdot 2 + 1 \cdot 4 + 1 \cdot 8 + 1 \cdot 16 + 0 \cdot 32 + 0 \cdot 64 + 1 \cdot 128 = 159$$

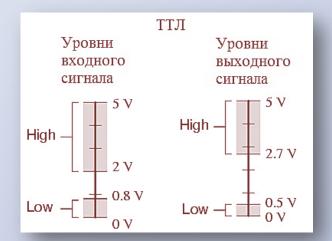

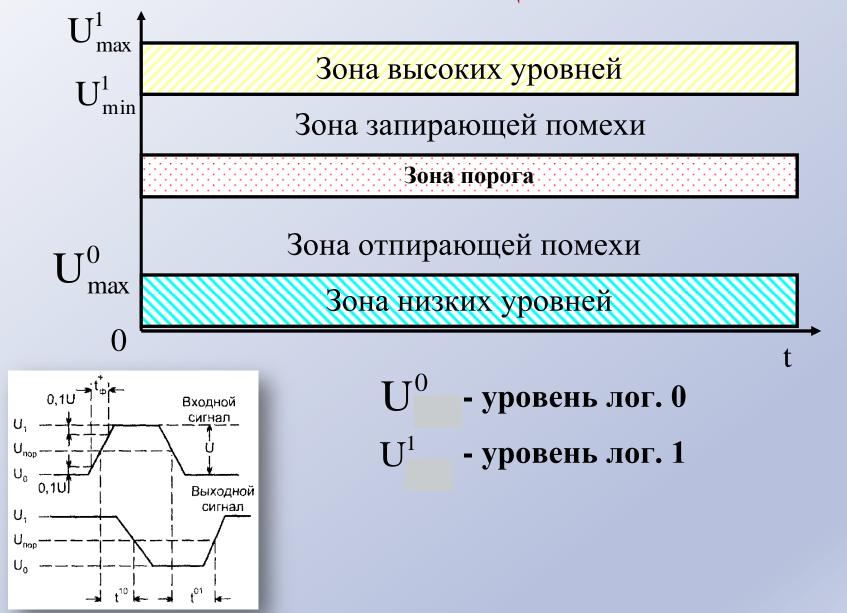

В современных цифровых устройствах (ЦУ) мы имеем дело лишь с двумя видами сигналов: логического 0 и логической 1.

Эти цифровые сигналы обычно представляются в потенциальной форме с положительной логикой сигналов, когда сигналу **логического 0** соответствует **положительное постоянное напряжение низкого уровня**, а сигналу **логической 1 – положительное постоянное напряжение более высокого уровня**.

В ЦУ: основа работы – двоичная система счисления, а выдача информации, например, в компьютеры – шестнадцатеричная.

| Десятичная<br>система | Двоичная<br>система | Восьмеричная<br>система | Шестнадцатеричная<br>система |

|-----------------------|---------------------|-------------------------|------------------------------|

| 1                     | 1                   | 1                       | 1                            |

| 2                     | 10                  | 2                       | 2                            |

| 3                     | 11                  | 3                       | 3                            |

| 4                     | 100                 | 4                       | 4                            |

| 5                     | 101                 | 5                       | 5                            |

| 6                     | 110                 | 6                       | 6                            |

| 7                     | 111                 | 7                       | 7                            |

| 8                     | 1000                | 10                      | 8                            |

| 9                     | 1001                | 11                      | 9                            |

| 10                    | 1010                | 12                      | A                            |

| 11                    | 1011                | 13                      | В                            |

| 12                    | 1100                | 14                      | С                            |

| 13                    | 1101                | 15                      | D                            |

| 14                    | 1110                | 16                      | E                            |

| 15                    | 1111                | 17                      | F                            |

| 16                    | 10000               | 20                      | 10                           |

| 17                    | 10001               | 21                      | 11                           |

| 18                    | 10010               | 22                      | 12                           |

# ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ (ЛЭ)

**Погические элементы** — это элементарные цифровые устройства, используемые для обработки информации в цифровой последовательности сигналов высокого — «1» и низкого — «0» уровней и выполняющие логические операции, а также различные комбинации этих операций.

<u>Таблица истинности -</u> это табличное представление логической (функциональной) схемы в котором перечислены все возможные сочетания значений входных сигналов вместе со значением выходного сигнала для каждого из этих сочетаний.

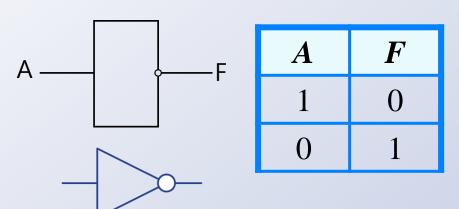

# Логический элемент НЕ (инвертор)

*Инвертор* – логический элемент **HE**, реализующий операцию отрицания

$$F = \overline{A}$$

Если на входе элемента 0, то на выходе 1 и наоборот

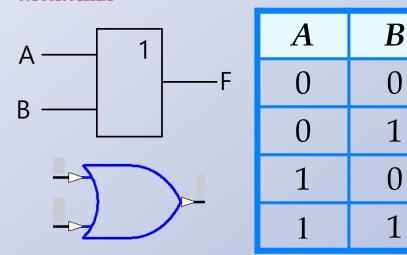

# Логический элемент ИЛИ (дизъюнктор)

**Дизъюнктор** – логический элемент **ИЛИ**, реализующий операцию логического сложения

()

$$F = A \cup B = A + B$$

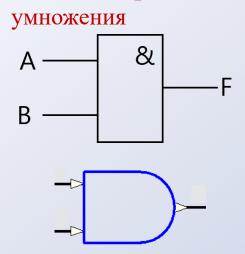

# Логический элемент И (конъюнктор)

Конъюнктор – логический элемент И, реализующий операцию логического

| $\boldsymbol{A}$ | В | F |

|------------------|---|---|

| 0                | 0 | 0 |

| 0                | 1 | 0 |

| 1                | 0 | 0 |

| 1                | 1 | 1 |

$$F = A \cap B = A \cdot B$$

Единица на выходе этого элемента появится только тогда, когда на всех входах будут единицы.

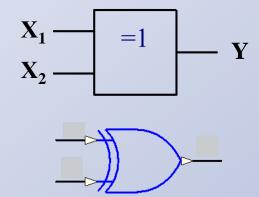

# Логический элемент «Исключающее ИЛИ»

#### «XOR», «eXclusive OR»

| $X_1$ | $X_2$ | Y |

|-------|-------|---|

| 0     | 0     | 0 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

$$Y = X_1 \oplus X_2$$

$$Y = X_1 \overline{X_2} + \overline{X_1} X_2$$

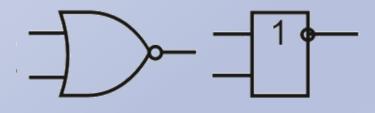

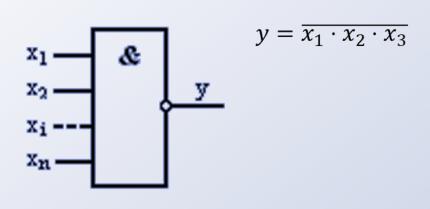

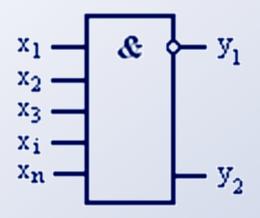

#### Логический элемент И-НЕ

**Логический элемент И-НЕ** выполняет логическую функцию <u>штрих Шеффера (И-НЕ),</u> он имеет, как минимум, два входа. На функциональных схемах он обозначается:

| $X_1$ | $X_2$ | Y |

|-------|-------|---|

| 0     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

$$Y = \overline{X_1 \cdot X_2}$$

#### Логический элемент ИЛИ-НЕ

**Логический элемент ИЛИ-НЕ** выполняет логическую функцию <u>стрелка Пирса (И-НЕ),</u> он имеет, как минимум, два входа. На функциональных схемах он обозначается:

$$Y_1 = \overline{X_1 + X_2}$$

$Y_2 = \overline{Y_1}$   $Y_2 = X_1 + X_2$

| $X_1$ | $X_2$ | $Y_1$ |

|-------|-------|-------|

| 0     | 0     | 1     |

| 0     | 1     | 0     |

| 1     | 0     | 0     |

| 1     | 1     | 0     |

#### ЛЭ (по виду реализуемой логической функции)

#### функциональные элементы одноступенчатой логики

#### функциональные элементы двухступенчатой логики

простейшие ЛЭ, реализующие функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ

реализующие более сложные функции: И-ИЛИ, ИЛИ-И, НЕ-И-ИЛИ, И-ЙЛИ-НЕ, И-ИЛИ-И и др.

статические

напряжение питания, уровни логических нуля и единицы, логический перепад, токи

ПАРАМЕТРЫ ЛЭ

динамические

быстродействие, определяемое скоростями перехода из одного состояния в другое

#### набор логических функций

число входов по И и по ИЛИ

коэффициент разветвления по выходу

потребляемая мощность

динамические параметры: задержка распространения сигнала и (или) максимальная частота входного сигнала

#### ТИПЫ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

#### ТИПЫ ТРАНЗИСТОРНЫХ ЛОГИК

#### транзисторнотранзисторная логика (ТТЛ)

Базовый логический элемент серий ТТЛ является элементом Шеффера (элемент И—НЕ) и реализует операцию, логическое умножение с отрицанием. Он представляет собой двоичный логический элемент, на выходе которого всегда единица, кроме случая, когда на все входы одновременно подаются логические единицы.

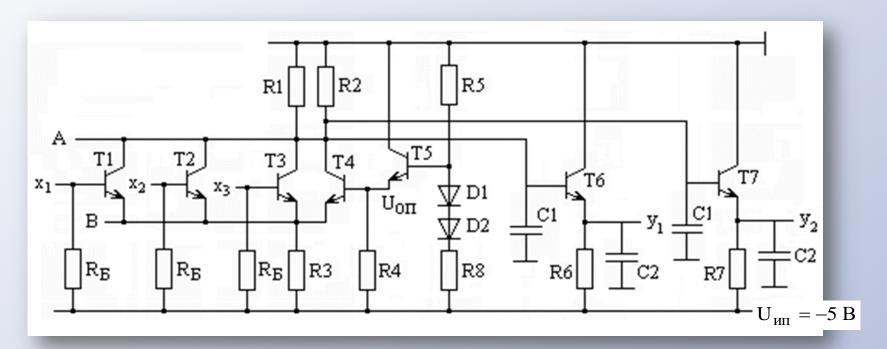

#### эмиттерносвязанная логика (ЭСЛ)

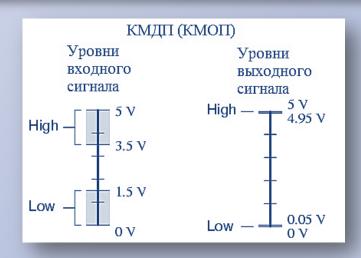

транзисторная логика на комплементарных ключах (КМДП (КМОП))

Эмиттерно-связанная логика (ЭСЛ) — один из вариантов логических схем, работающих в ненасыщенном режиме. ЭСЛ-схемы имеют низкий выходной импеданс, небольшой разброс уровней логического напряжения и хорошую помехоустойчивость для обоих уровней логического напряжения.

В зависимости от способа кодирования входной информации («1» и «0») эта схема может реализовать

- либо функции ИЛИ–НЕ, ИЛИ для положительной логики,

- либо функции И–НЕ, И для отрицательной логики.

# СОГЛАШЕНИЕ О ЦИФРОВОМ ПРЕДСТАВЛЕНИИ ИНФОРМАЦИИ

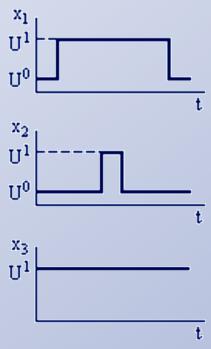

# Транзисторно-транзисторная логика (ТТЛ)

| $x_{I}$ | $x_2$           | $x_3$ | y |

|---------|-----------------|-------|---|

| 0       | $\frac{x_2}{0}$ | 0     | 1 |

| 0       | 0               | 1     | 1 |

| 0       | 1               | 0     | 1 |

| 0       | 1               | 1     | 1 |

| 1       | 0               | 0     | 1 |

| 1       | 0               | 1     | 1 |

| 1       | 1               | 0     | 1 |

| 1       | 1               | 1     | 0 |

|         |                 |       |   |

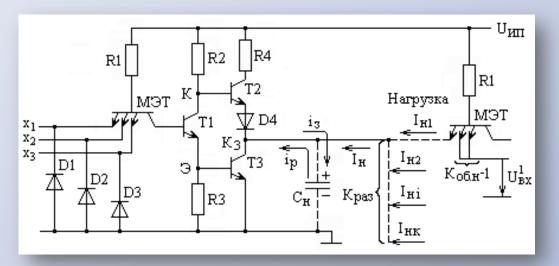

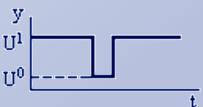

Схема электрическая принципиальная элемента «И-НЕ» ТТЛ

Схема состоит из двух частей:

- Первая часть входная, реализующая функцию И, содержит резистор R1 и МЭТ;

- ▶ Вторая часть выходная, реализующая функцию НЕ, содержит сложный инвертор на транзисторах T1-T2.

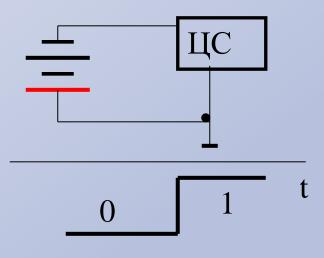

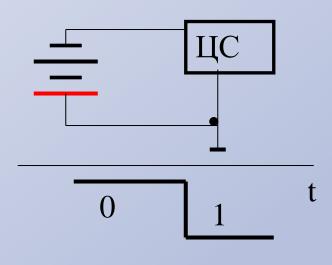

#### ПОЛОЖИТЕЛЬНАЯ ЛОГИКА

Цифровые сигналы обычно представляются в потенциальной форме **с положительной логикой сигналов**, когда <u>сигналу</u> <u>логического 0 соответствует положительное постоянное напряжение низкого уровня</u>, а <u>сигналу логической 1 — положительное постоянное напряжение более высокого уровня</u>.

Если состояние 1 определяет ВЫСОКИЙ уровень, а состояние 0 определяет НИЗКИЙ уровень, то такая логика называется положительной.

#### полярность напряжения питания:

#### положительная

# о ЦС t

#### отрицательная

ЦС-цифровая схема

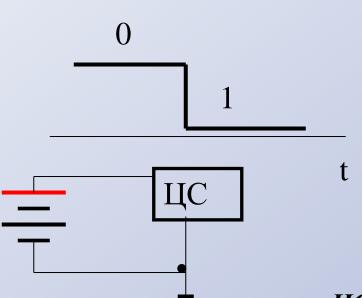

# ОТРИЦАТЕЛЬНАЯ ЛОГИКА

Если состояние 1 определяет НИЗКИЙ уровень, а состояние 0 определяет ВЫСОКИЙ уровень, то такая логика называется отрицательной.

#### полярность напряжения питания:

#### положительная

## отрицательная

ЦС-цифровая схема

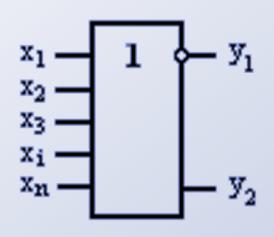

# Эмиттерно-связанная логика (ЭСЛ)

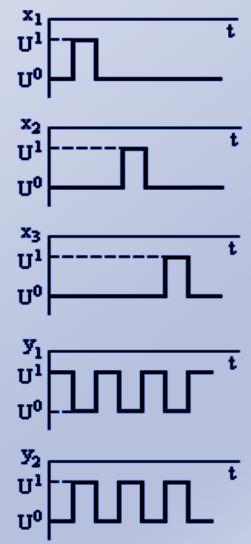

Элемент реализует для "положительной логики" одновременно функции ИЛИ–НЕ (стрелка Пирса) по выходу  $y_1$  и функцию ИЛИ (дизьюнкция) по выходу  $y_2$ .

| $y_1$ | = | $\overline{x_1}$ | + | $\overline{x_2}$ | + | $\overline{x_3}$ | ; |

|-------|---|------------------|---|------------------|---|------------------|---|

$$y_2 = x_1 + x_2 + x_3.$$

| $x_1$ | $x_2$ | $x_3$ | $y_1$ | $y_2$ |

|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     |

| 0     | 0     | 1     | 0     | 1     |

| 1     | 1     | 0     | 0     | 1     |

| 1     | 0     | 1     | 0     | 1     |

| 0     | 1     | 1     | 0     | 1     |

| 1     | 1     | 1     | 0     | 1     |

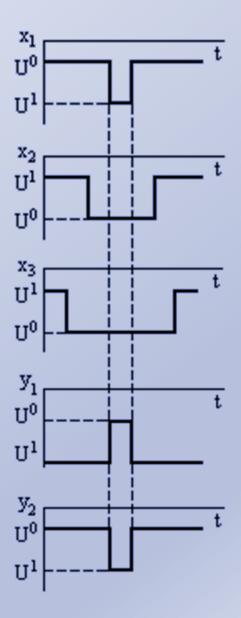

Элемент реализует для "отрицательной логики" одновременно функции U–HE по выходу  $y_1$  и функцию U по выходу  $y_2$ .

$$y_1 = \overline{x_1 \cdot x_2 \cdot x_3};$$

$$y_2 = x_1 \cdot x_2 \cdot x_3.$$

| $x_1$ | $x_2$ | $x_3$ | $y_1$ | $y_2$ |

|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     |

| 0     | 1     | 0     | 1     | 0     |

| 0     | 0     | 1     | 1     | 0     |

| 1     | 1     | 0     | 1     | 0     |

| 1     | 0     | 1     | 1     | 0     |

| 0     | 1     | 1     | 1     | 0     |

| 1     | 1     | 1     | 0     | 1     |

#### Схема электрическая принципиальная элемента ЭСЛ

Для положительной логики «1» и «0» представляются напряжениями:

$$U^0 = -1,45 \div 1,9 B$$

$$U^1 = -1,45 \div 0,95 B$$

Для отрицательной логики «1» и «0» представляются напряжениями:

$$U^0 = 0.7 \div -0.95 \text{ B}$$

$$U^1 = -1,45 \div -1,9 B$$

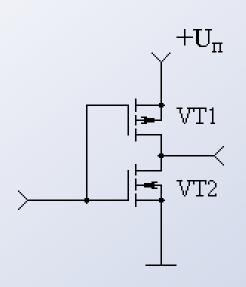

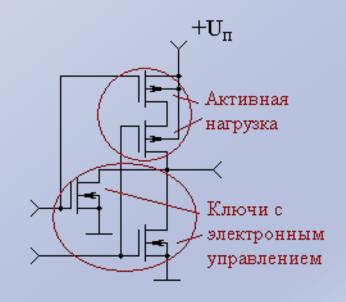

## Транзисторная логика на комплементарных ключах (КМОП)

Микросхемы на комплементарных МОП транзисторах (КМОП-микросхемы) строятся на основе МОП транзисторов с n- и p-каналами.

При формировании **логической единицы** открыт верхний транзистор, а нижний закрыт. В результате ток через КМОП схему не протекает.

*При формировании логического нуля открыт нижний транзистор, а верхний закрыт.* И в этом случае ток от источника питания через микросхему не протекает.

«2И-НЕ» «ИЛИ-НЕ»

#### ЦИФРОВЫЕ УСТРОЙСТВА

Устройства с жёсткой логикой работы

Устройства с программируемым алгоритмом работы

выходные сигналы в каждый момент жёстко определяются входными сигналами и это соответствие не может быть изменено

соответствие выходных сигналов входным сигналам может быть изменено программой — набором управляющих кодов

быстрее, проще для простых функций, сложнее в разработке

медленнее, проще для сложных функций, проще в разработке

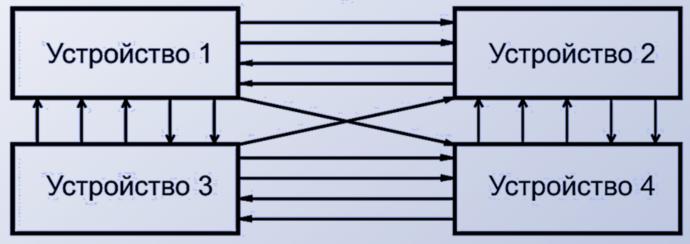

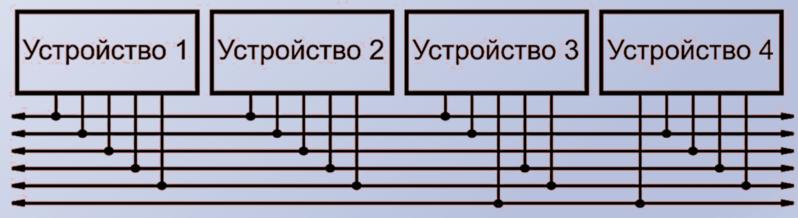

# ТИПЫ ОРГАНИЗАЦИИ СВЯЗЕЙ в цифровых устройствах

# Классическая организация связей

# Шинная организация связей

# КЛАССИФИКАЦИЯ цифровых устройств

#### По способу функционирования ЦУ

#### Комбинационные ЦУ

(не обладающие памятью)

т.е. не способные запоминать результаты выполненных операций. Здесь значения сигналов на выходах (выходное кодовое слово) определяются только совокупностью сигналов на входах (входным кодовым словом) в данный момент времени.

операций и хранить эту информацию на своих выходах в виде кодовых слов. У них значение выходного кодового слова определяется не только входным кодовым словом в данный момент времени, но и хранившимся на выходах кодовым словом в предыдущий момент времени.

способные запоминать результаты выполненных

Последовательностные ЦУ

(устройства с памятью)

Триггер, шифратор, дешифратор, мультиплексор, демультиплексор

Счетчик, регистр

#### Функциональные узлы комбинационного типа

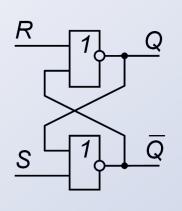

**Триггер** — устройство, имеющие два устойчивых состояния и способное под действием управляющих сигналов скачком переходить из одного устойчивого состояния в другое.

Два типа: асинхронные и синхронные.

*RS*-триггер с прямыми входами:

T

R

$$Q_{n+1} = f(S_n, R_n, Q_n)$$

$$Q_{n+1} = S_n + \overline{R_n} Q_n$$

| $S_{\rm n}$ | $R_{\rm n}$ | $Q_{\rm n}$ | $Q_{n+1}$ |

|-------------|-------------|-------------|-----------|

| 0           | 0           | 0           | 0         |

| 0           | 0           | 1           | 1         |

| 0           | 1           | 0           | 0         |

| 0           | 1           | 1           | 0         |

| 1           | 0           | 0           | 1         |

| 1           | 0           | 1           | 1         |

| 1           | 1           | 0           | X         |

| 1           | 1           | 1           | X         |

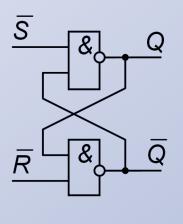

#### *RS*-триггер с инверсными входами

$$Q_{n+1} = f(S_n, R_n, Q_n)$$

$$Q_{n+1} = \overline{S_n} + R_n Q_n$$

| $S_{\rm n}$ | $R_{\rm n}$ | $Q_{\rm n}$ | $Q_{n+1}$ |

|-------------|-------------|-------------|-----------|

| 0           | 0           | 0           | X         |

| 0           | 0           | 1           | X         |

| 0           | 1           | 0           | 1         |

| 0           | 1           | 1           | 1         |

| 1           | 0           | 0           | 0         |

| 1           | 0           | 1           | 0         |

| 1           | 1           | 0           | 0         |

| 1           | 1           | 1           | 1         |

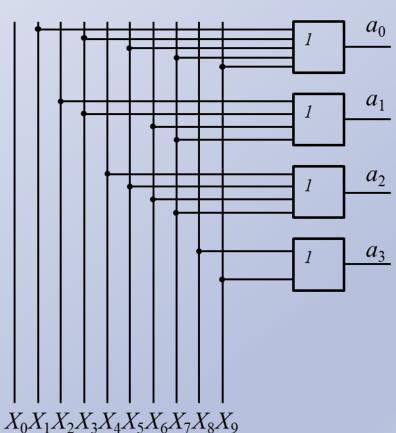

**Шифратор** — функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в п-разрядный двоичный код.

| число | $a_3$ | $a_2$ | $a_1$ | $a_0$ |

|-------|-------|-------|-------|-------|

| $X_0$ | 0     | 0     | 0     | 0     |

| $X_1$ | 0     | 0     | 0     | 1     |

| $X_2$ | 0     | 0     | 1     | 0     |

| $X_3$ | 0     | 0     | 1     | 1     |

| $X_4$ | 0     | 1     | 0     | 0     |

| $X_5$ | 0     | 1     | 0     | 1     |

| $X_6$ | 0     | 1     | 1     | 0     |

| $X_7$ | 0     | 1     | 1     | 1     |

| $X_8$ | 1     | 0     | 0     | 0     |

| $X_9$ | 1     | 0     | 0     | 1     |

$$a_0 = X_1 + X_3 + X_5 + X_7 + X_9$$

$$a_1 = X_2 + X_3 + X_6 + X_7$$

$$a_2 = X_4 + X_5 + X_6 + X_7$$

$$a_3 = X_8 + X_9$$

**Дешифратор** - функциональный узел, предназначенный для преобразования п-разрядного двоичного кода в комбинацию управляющих выходных сигналов.

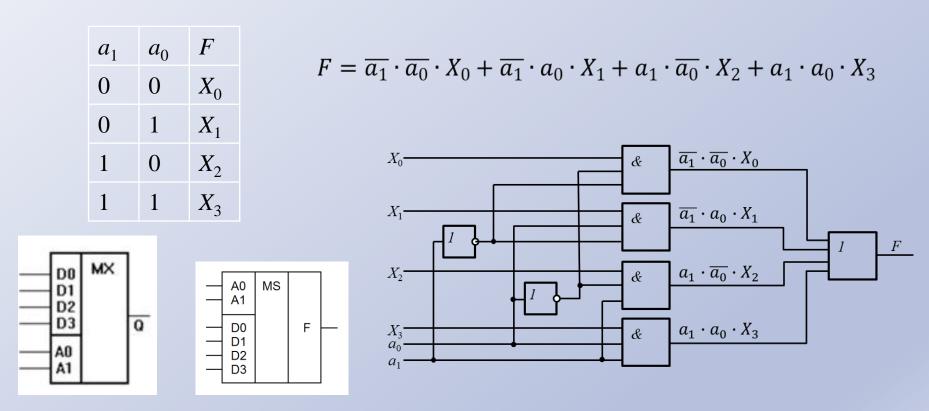

**Мультиплексор** - функциональный узел, который осуществляет управляемую коммутацию информации, поступающей по N входным линиям, на одну выходную линию. Коммутация определенной входной линии происходит в соответствии с двоичным адресным кодом.

Если адресный код имеет n разрядов, то можно осуществить  $N=2^n$  комбинаций адресных сигналов.

Рассмотрим n = 2, N = 4. F – значение информации.

Таблица функционирования будет следующей:

**Демультиплексор** - функциональный узел, осуществляющий управляемую коммутацию информации, поступающей по одному входу на один из N выходов.

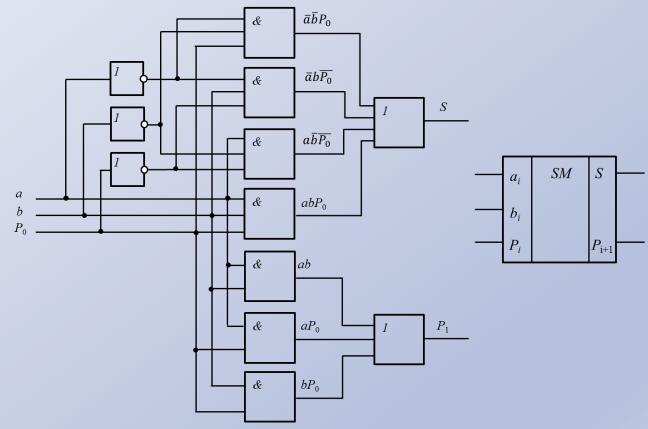

#### Сумматор - функциональный узел, выполняющий арифметическое сложение кодов двух чисел.

#### По количеству одновременно обрабатываемых разрядов складываемых чисел:

- одноразрядные,

- многоразрядные.

#### По числу входов и выходов одноразрядных двоичных сумматоров:

- четверть сумматоры;

- полусумматоры;

оборудование.

– полные одноразрядные двоичные сумматоры.

#### По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

- последовательные, в которых обработка чисел ведется поочередно, разряд за разрядом на одном и том же оборудовании;

- параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется свое

#### Функциональные узлы последовательностного типа

**Регистр -** функциональный узел, осуществляющий прием, хранение и передачу информации:

- » регистры с последовательным приемом и выдачей информации (сдвиговые регистры);

- » регистры с параллельным приемом и выдачей информации (регистры памяти).

**Счетчик** - функциональный узел, предназначенный для подсчета количества импульсов:

- > двоичные

- > недвоичные.

Основные параметры: коэффициент пересчета и быстродействие.

Коэффициент пересчета  $K_{\text{сч}}$  — максимальное число импульсов, которое может быть подсчитано данным счетчиком, и зависит от количества разрядов n ( $K_{\text{сч}} = 2^n$ ).

*Быстродействие* счетчика определяется двумя величинами: разрешающей способностью и временем установки очередного состояния. Разрешающая способность  $t_{\rm p}=1/f_{\rm cq}$  ( $f_{\rm cq}$  — частота следования входных импульсов) определяется минимально допустимым временным интервалом между двумя выходными импульсами, при котором не происходит потери счета (сбоя). Время установки представляет собой интервал времени между поступлением импульса на вход счетчика и переходом его в новое состояние.